- 2014/05會有第一個16 nm的Tape Out.2014全年還有另外15個Tape Out,而2015還有45個Tape Out.

- 10 nm FinFET是台積電第三代FinFET,Risk Production會在4Q 2015.

- 20nm SOC今年第4季營收占比將達20%,全年可達10%.

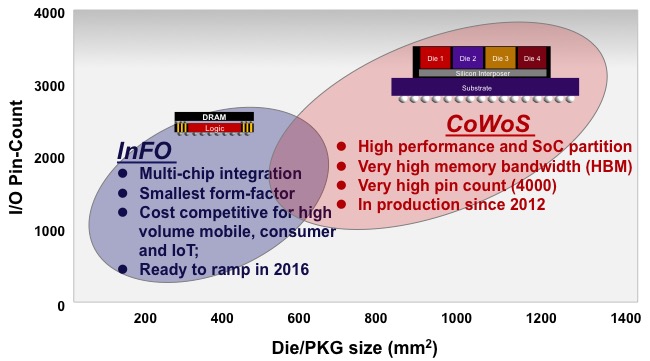

- CoWoS目前只有小量生產,因為成本的關係,CoWoS只適合用在高效能需求的晶片上.但為了解決成本的問題,台積電另外開發了低成本的InFO,InFO和高成本的CoWoS一樣,能連結不同的晶片,但成本卻低很多.

- 每支智慧手機對台積電貢獻度從2013年的7美元會增加到2014年的8美元.高階智慧手機對台積電貢獻度從2013年的10.8美元會增加到2014年的13.9美元.中階智慧手機對台積電貢獻度仍是6美元,低階智慧手機對台積電貢獻度仍是3.6美元.

- EUV仍未準備好,可能在10 nm已開始準備後,EUV才會進入..

- CC Wei didn’t reveal the differences between TSMC's InFO, Integrated FanOut, and CoWoS, Chip-on-Wafer-on-Substrate. (Please refer to Breakfast Bytes Blogs and Embedded WLP 2010 report: Next generations of IC packaging and substrate assembly waves in pddnet.com)

(source from Breakfast Bytes Blogs)

(source from www.prlog.org)

- 成熟製程如40、45奈米 for finger print IC明顯有產能不足的現像,但台積電不會再投資在成熟製程,會持續以去瓶頸化等其他方式來增加產能.

- 在Customer Concentration Risk上,劉德音說不只是台積電會擔心這個挑戰,反過來看,客戶自己本身也會同樣擔心訂單下個同一個廠商,而導致訂單過度集中的問題,所以,要解決這個問題,台積電必須和客戶密切合作,一起來面對這個挑戰.

- 單一客戶(意指Apple)吃掉今年80%的20奈米產能,若到明年該客戶轉移到16奈米時,20奈米產能不是會過剩嗎?關於這個問題,劉德音說這名客戶明年還是會繼續使用20奈米.

- 關於Design Portability讓客戶能找其他晶圓廠代工的問題,魏哲家認為Delayer or Reverse Engineering是無法知道IC的製造過程,製程無法單純被Copy,劉德音認為Porting的成本會隨著製程演進而不斷增加,而且,即便20奈米和16奈米有相同的Design Rule,讓其他的晶圓代工廠有時間揣摩台積電的製程,但台積電今天的製程不等於明天的製程,台積電會不斷精進,所以即便有相同的Design Rule,競爭對手也不容易跟上.

沒有留言:

張貼留言